- Doctorate / Master Degree Program

- Fellowship Program

- Advanced Certificate Medical Program

- PG Diploma

- SAP Program

- Data Science & AI

- Salesforce Training

- HR & Finance Training

Doctorate / Master Degree Program

✕

Doctorate / Master Degree Program

Birchwood University

EIMT

London School of Management and Technology | LSMT

Fellowship Program

Advanced Certificate Medical Program

PG Diploma

SAP Program

Data Science & AI

Salesforce Training

HR & Finance Training

Download your Brochure

Fill out the application form and download the brochure for joining our program.

https://youtu.be/_KW9ZKQYtNY?si=wrMtMBnFXZk5IJ3c

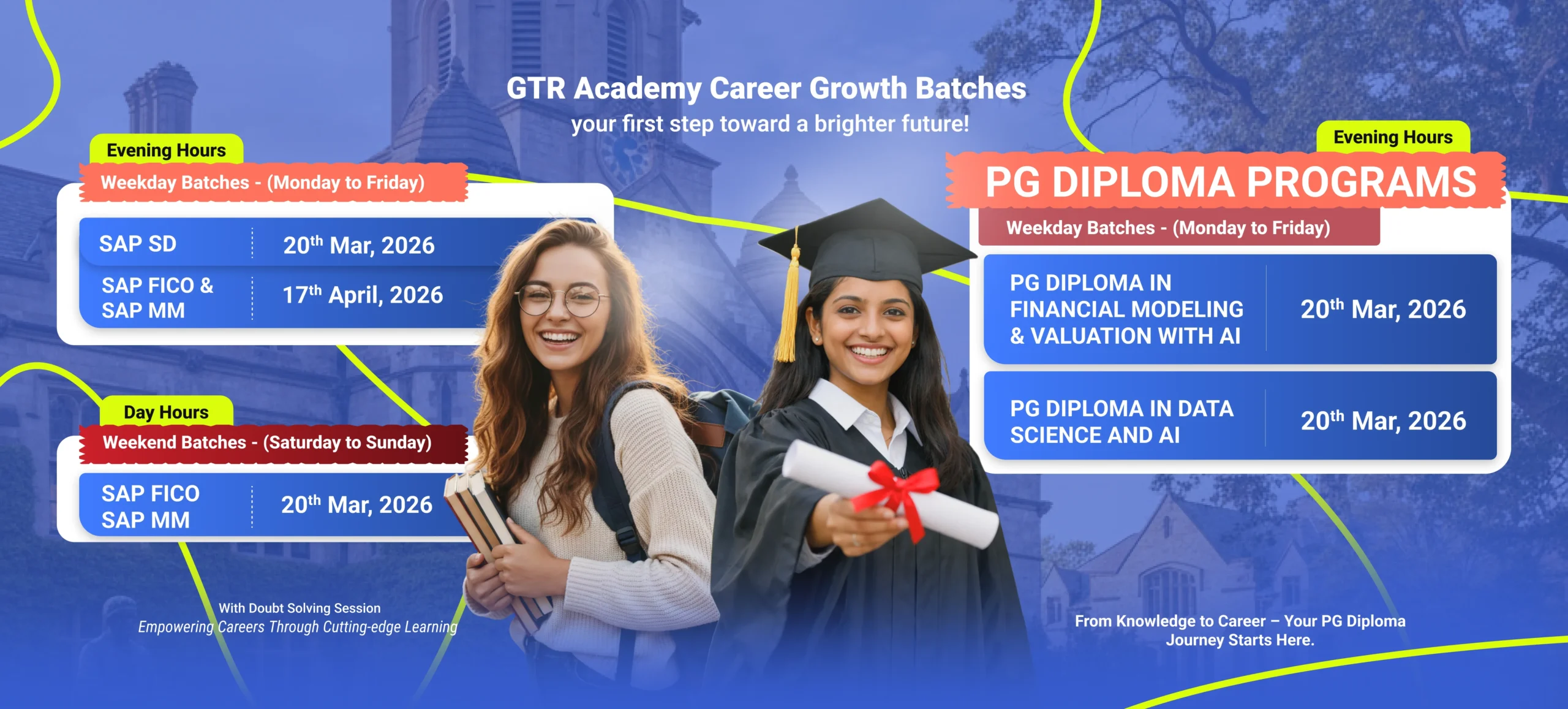

UPCOMING BATCHES

SAP FICO

Weekday Batch

29th Aug

🗓️ Monday & Friday | ⏰ 10:00 AM - 12:00 PM

SAP FICO

Weekend Batch

31nd August

🗓️ Saturday & Sunday | ⏰ 3:00 PM - 5:00 PM

SAP MM

Weekday Batch

29th August

🗓️ Monday - Friday | ⏰ 7:00 PM - 9:00 PM

SAP MM

Weekend Batch

31th August

🗓️ Saturday & Sunday | ⏰ 3:00 PM - 5:00 PM

SAP BTP

Weekend Batch

31th August

🗓️ Saturday & Sunday | ⏰ 3:00 PM - 5:00 PM

SAP TM

Weekend Batch

7th September

🗓️ Saturday & Sunday | ⏰ 3:00 PM - 5:00 PM

SAP FIORI

Weekend Batch

7th September

🗓️ Saturday & Sunday | ⏰ 3:00 PM - 5:00 PM

https://youtu.be/IoG1WxAKXwg

https://www.youtube.com/watch?v=l9XB4Gwt0H4

https://www.youtube.com/watch?v=71Y_1M0NSoo

https://www.youtube.com/watch?v=yjGQ1g9S-dU

https://www.youtube.com/watch?v=Q_BixayJrHk

https://www.youtube.com/watch?v=jqOVYf7ESh0