Best Multicycle Path in VLSI, 2025: A Complete Beginner’s Guide

As we step deeper into the semiconductor revolution of 2025, digital circuit design is becoming more complex and timing-critical than ever. One of the most essential yet misunderstood concepts in Very Large Scale Integration (VLSI) is the Multicycle Path in VLSI. For entry-level IT professionals aiming to understand timing optimization and digital design, grasping this concept is a must.

In this blog, we’ll break down the multicycle path in VLSI step-by-step, explore its relationship with false paths, learn how it affects setup and hold constraints, and provide real-world use cases and examples. Whether you’re searching for a multicycle path in VLSI PDF, or looking to understand a set multicycle path example, this comprehensive guide will simplify it all.

What is a Multicycle Path in VLSI?

In digital circuit design, especially during Static Timing Analysis (STA), a multicycle path in VLSI refers to a data path that is intentionally allowed to take more than one clock cycle to propagate from the source register to the destination register. Unlike typical timing paths that are evaluated in a single clock cycle, multicycle paths are designed to function across multiple cycles to ease timing constraints.

These paths are often found in complex arithmetic operations or in control logic where immediate data transfer isn’t necessary every clock cycle.

Why Are Multicycle Paths Important in 2025?

As modern chips now integrate AI engines, 5G modules, and GPU cores onto the same die, timing closure becomes harder. A multicycle path in VLSI is a powerful tool that designers use to optimize performance and manage long combinational logic delays without increasing the clock period.

In 2025, with the rise of high-frequency SoCs (System on Chips), defining multicycle path constraints is more critical than ever for achieving power and performance efficiency.

Multicycle Path Setup and Hold: Understanding the Basics

Timing constraints in VLSI are defined in terms of setup and hold times. In conventional designs, data needs to reach its destination within one clock cycle. But for a multicycle path, the constraints are relaxed.

Setup Time for Multicycle Paths

When a path is declared as multicycle, the setup check is shifted forward by the number of cycles you allow. For example, if you define a 2-cycle multicycle path, the STA tool will allow the data to arrive in two cycles instead of one.

Hold Time for Multicycle Paths

Hold timing constraints are typically addressed by applying negative clock skew, moving the capture edge earlier to guarantee signal stability during the critical initial clock phase. If not handled correctly, hold violations can cause functional failure.

Many engineers use commands like set_multicycle_path -setup and set_multicycle_path -hold in tools like Synopsys Design Compiler or PrimeTime.

False Path vs. Multicycle Path in VLSI

In VLSI design, a false path refers to a signal route that can be ignored during timing verification since it remains inactive under normal operating conditions. In contrast, a multicycle path does transfer data, but it does so over multiple cycles.

It’s common to see both constraints defined in STA scripts:

False paths: Removed from timing analysis

Multicycle paths: Retimed over multiple cycles

Understanding the difference is vital when you analyze false path and multicycle path in VLSI designs. Mistaking one for the other can lead to functional bugs.

Real-World Multicycle Path Example

Consider a case where a division operation requires three clock cycles to complete. Rather than increasing the global clock period (which slows down your entire chip), you can define the output path of the divider as a 3-cycle multicycle path. This allows the logic to complete without requiring tighter logic synthesis or slower clocks.

This multi-cycle path in VLSI example demonstrates why this concept is a key timing optimization tool in complex VLSI systems.

Half Cycle Path in VLSI: A Special Case

Another timing exception is the half cycle path in VLSI, where setup or hold checks are done on half the clock cycle. This is commonly used in clock-domain crossing and latch-based designs. While not the same as multicycle paths, both concepts manipulate timing windows to ensure signal stability and correctness.

How to Set Multicycle Path Constraints

Using timing tools, designers apply multi cycle path constraints with specific commands. For instance:

This instructs the tool to evaluate the path with adjusted timing checks, offering more flexibility and enabling higher performance in your design.

If you’re studying set multicycle path example use cases, start with the division operation or slow memory fetch scenarios.

Common Mistakes in Handling Multicycle Paths

Forgetting to adjust hold time – Designers often define multicycle setup paths but forget the corresponding hold adjustment, leading to potential hold violations.

Incorrect path analysis – Not all slow paths should be declared as multicycle. Misuse can mask genuine timing failures.

Tool misconfiguration – Improper tool commands or incorrect clock definitions can lead to skipped checks.

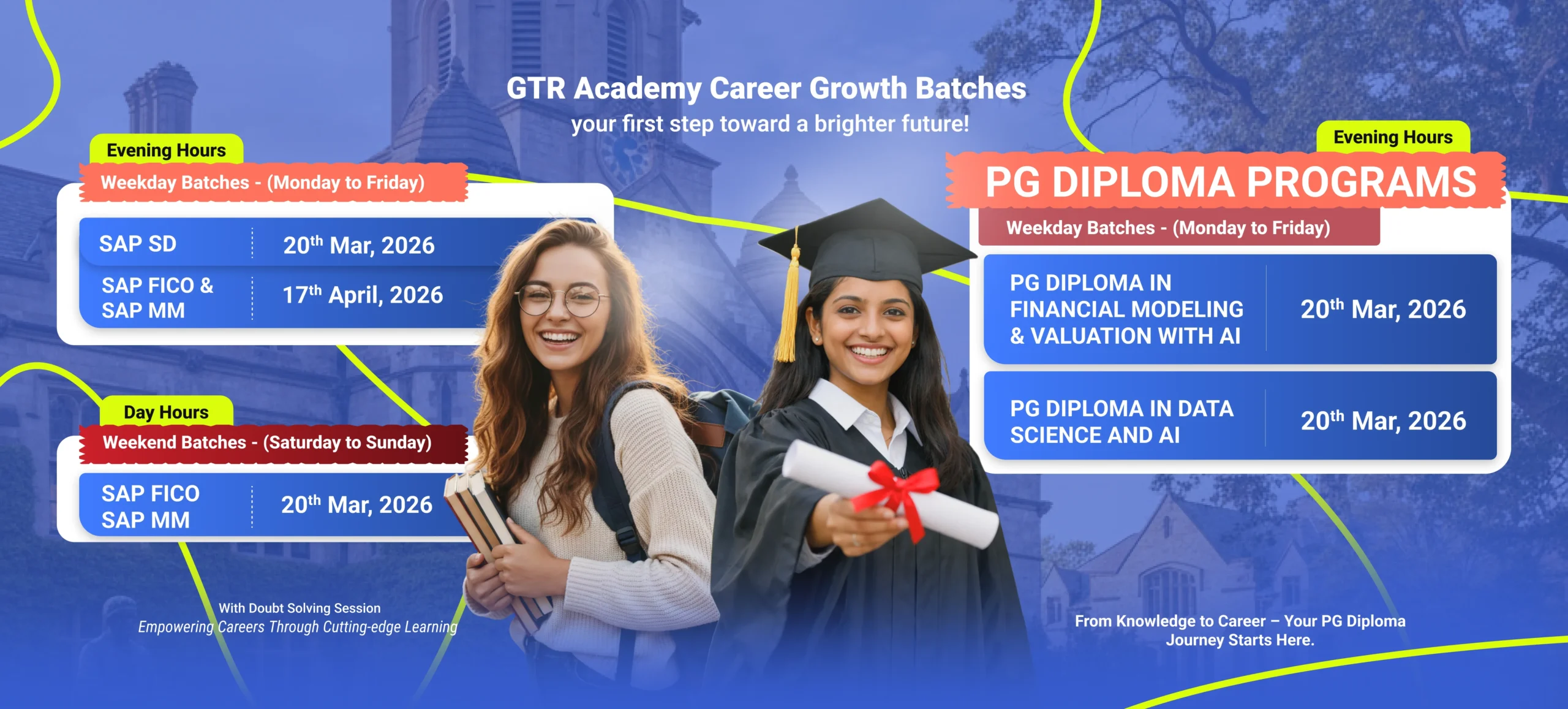

That’s why formal training, like the one offered at GTR Academy, is essential. They provide real-time labs and industry-relevant modules focused on STA, timing exceptions, and backend design, helping you understand these tricky scenarios in depth.

Multicycle Path in VLSI PDF and Resources

Searching for resources like multicycle path in VLSI PDF, fabrication process in VLSI, or false path and multicycle path in VLSI Slideshare can be helpful, but hands-on learning is key. These concepts require both theoretical understanding and practical simulation, and that’s where structured training from GTR Academy makes all the difference.

Why Learn Multicycle Paths in 2025?

Chip design in 2025 is ruled by complex clocking structures, power domains, and multiple IP integrations. Understanding multicycle path in VLSI is essential for:

Backend VLSI engineers

STA and physical design professionals

ASIC verification engineers

Conclusion: Take the Right Path—Multicycle!

The multicycle path in VLSI is more than just a timing trick—it’s a strategic design choice that enables optimized performance in today’s high-speed chips. From learning how to apply setup and hold constraints to differentiating them from false paths, this knowledge bridges your understanding of theory and real-world chip implementation.

Whether you’re reviewing multicycle paths in VLSI with PDF diagrams, exploring use cases, or setting constraints in an STA tool, this concept will guide your success in VLSI design workflows.

Ready to dive deeper into multicycle paths, STA, and real-time chip implementation?

Enroll in a certified VLSI program at GTR Academy and start building your expertise today.

I am a skilled content writer with 5 years of experience creating compelling, audience-focused content across digital platforms. My work blends creativity with strategic communication, helping brands build their voice and connect meaningfully with their readers. I specialize in writing SEO-friendly blogs, website copy, social media content, and long-form articles that are clear, engaging, and optimized for results.

Over the years, I’ve collaborated with diverse industries including technology, lifestyle, finance, education, and e-commerce adapting my writing style to meet each brand’s unique tone and goals. With strong research abilities, attention to detail, and a passion for storytelling, I consistently deliver high-quality content that informs, inspires, and drives engagement.