Best Clock Latency in VLSI, 2025 – Everything Beginners Need to Know

As semiconductor technology advances at an unprecedented pace, clock latency has emerged as a pivotal consideration in modern VLSI design methodologies. For every aspiring engineer or entry-level IT professional looking to break into VLSI in 2025, understanding clock latency is essential. Whether you’re preparing for interviews, diving into timing analysis, or simply trying to build foundational knowledge, this article provides a clear and beginner-friendly explanation.

In this guide, we’ll cover what clock latency in VLSI is, its types, real-world examples, how to fix clock latency in VLSI, and how it connects to related concepts like clock skew, insertion delay, network latency, and clock uncertainty. So let’s break it down.

What is Clock Latency in VLSI?

Clock latency in VLSI refers to the time it takes for the clock signal to propagate from the clock source (such as a phase-locked loop or PLL) to the clock pin of a flip-flop. In simpler terms, it measures how long it takes for the clock signal to reach its destination in the circuit.

Modern digital systems rely on precise clock edges to regulate data movement through pipelines and state machines. So, even a small delay in clock delivery—i.e., clock latency—can impact overall performance, timing closure, and chip reliability.

Types of Clock Latency in VLSI

Understanding the types of clock latency helps you visualize how delays affect circuit behavior. There are two main categories:

1. Source Latency

Clock insertion delay quantifies the signal latency between the clock source and the first branching point in the distribution network.

It includes delays introduced by buffers and wires before reaching the network.

2. Network Latency

This is the time it takes from the starting point of the clock network to the clock pin of the sequential elements, like flip-flops or latches.

This delay is affected by clock tree synthesis, routing congestion, and network complexity.

Together, source latency and network latency in VLSI define the complete path that contributes to clock latency.

Clock Latency in VLSI Example

Let’s say a clock signal originates from a PLL and travels through a series of buffers and wires to reach a flip-flop. Suppose:

The source latency is 80 ps (picoseconds).

The network latency is 120 ps.

Then the total clock latency is 80 ps + 120 ps = 200 ps.

This 200 ps delay needs to be factored into the setup and hold timing analysis to ensure the chip functions correctly.

Why Clock Latency Matters in VLSI Design

In modern VLSI systems, where chips are packed with billions of transistors, even nanosecond-level timing issues can cause data corruption, logic failure, or power inefficiencies. That’s why clock latency in VLSI is one of the first things timing engineers analyze and optimize.

Incorrect or unbalanced latency can lead to:

Timing violations

Clock skew

Functional errors

Tools like PrimeTime, Tempus, and Innovus are used to analyze and fix latency-related issues during static timing analysis (STA) and clock tree synthesis (CTS).

How to Fix Clock Latency in VLSI

Fixing clock latency involves a combination of design strategies, clock tree balancing, and tool-based optimizations. Here’s how engineers typically handle it:

1. Clock Tree Synthesis (CTS)

Design tools build a balanced clock tree to ensure minimal and equal latency to all endpoints.

2. Buffer Insertion

Engineers strategically insert buffer cells in clock distribution networks to precisely manage signal propagation delays.

3. Skew Balancing

Engineers balance clock network delays to minimize timing differences between sequential elements, maintaining synchronisation across all signal paths.

4. Avoiding Congested Routes

Engineers strategically optimize component placement and interconnect routing to minimize signal delays resulting from network congestion.

5. Using Advanced Nodes and Techniques

Modern tools and technologies reduce wire parasitics and buffer overheads, thus minimizing latency.

By following these practices, designers can effectively fix clock latency in VLSI and improve the chip’s reliability.

Insertion Delay in VLSI

Insertion delay is another term often used synonymously with clock latency. Specifically, it refers to the delay from the clock source to the clock pin of the register. In essence, insertion delay = clock latency.

In timing analysis reports, you’ll often find insertion delay values listed for every clock path endpoint, helping engineers detect areas that may need adjustment.

Skew and Latency in VLSI

While clock latency is the delay from source to sink, clock skew refers to the difference in arrival times of the clock signal at two different flip-flops.

Together, skew and latency in VLSI determine if a design meets timing:

High latency + high skew = possible setup or hold violations

Balanced latency + minimal skew = optimal timing

Engineers aim for zero or positive skew during clock tree design, using controlled latency to their advantage.

Clock Uncertainty in VLSI

Another closely related concept is clock uncertainty, which accounts for the variations or inaccuracies in clock arrival time. It includes factors like:

Jitter

Skew

Tool margin

High clock uncertainty forces designers to budget more time in the timing path, making it harder to meet timing closure. Maintaining consistent clock network delays enables more accurate timing predictions and reduces design margin requirements.

Network Latency in VLSI

As mentioned earlier, network latency in VLSI forms a major part of overall clock latency. It is influenced by:

Clock net topology

Buffer strength

Wire length

Congestion levels

By analyzing network latency, designers can pinpoint delays in the distribution system and optimize accordingly.

Clock Skew in VLSI

Clock skew is another vital concept tightly linked to clock latency. Skew occurs when different endpoints receive the same clock signal at slightly different times due to unequal clock latency.

In VLSI design, skew is classified as:

Positive Skew – Receiving flip-flop gets clocked after the sending flip-flop.

Negative Skew – Receiving flip-flop gets clocked before the sending flip-flop.

Conclusion

In summary, clock latency in VLSI is a key timing parameter that affects how clock signals reach various components in a digital circuit. Understanding the nuances of source latency, network latency, insertion delay, skew, and uncertainty is vital for every digital designer or timing engineer.

Mastering clock latency analysis and optimization techniques represents a core competency in reliable VLSI implementation, spanning from initial characterization to final timing closure. As VLSI designs grow more complex in 2025, mastering clock latency is no longer optional—it’s essential.

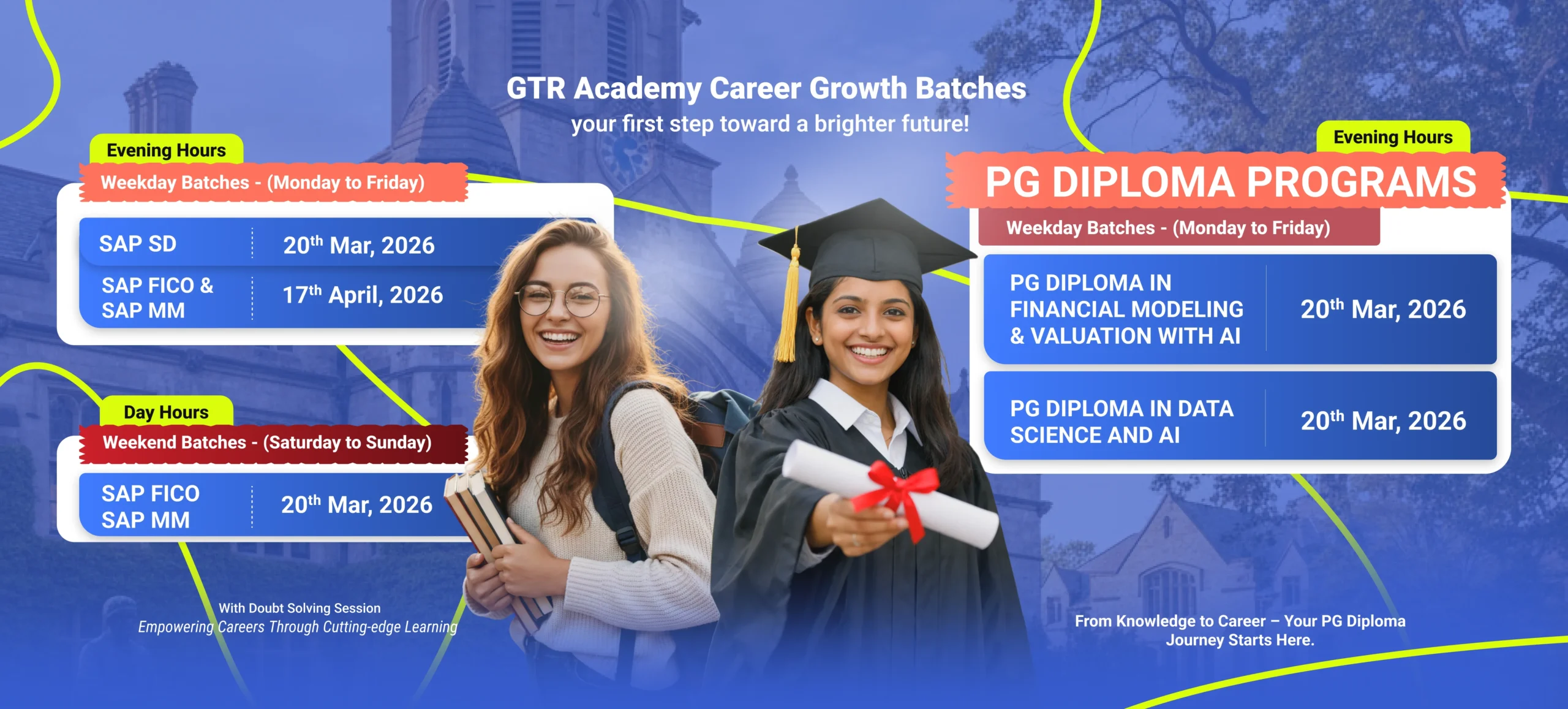

If you’re eager to learn more and gain hands-on experience in timing analysis, clock tree synthesis, and physical design, check out GTR Academy—India’s leading training institute for VLSI and chip design courses tailored for freshers and professionals.

I am a skilled content writer with 5 years of experience creating compelling, audience-focused content across digital platforms. My work blends creativity with strategic communication, helping brands build their voice and connect meaningfully with their readers. I specialize in writing SEO-friendly blogs, website copy, social media content, and long-form articles that are clear, engaging, and optimized for results.

Over the years, I’ve collaborated with diverse industries including technology, lifestyle, finance, education, and e-commerce adapting my writing style to meet each brand’s unique tone and goals. With strong research abilities, attention to detail, and a passion for storytelling, I consistently deliver high-quality content that informs, inspires, and drives engagement.