Temperature Inversion in VLSI, 2025 – Understanding the Impact on Best Chip Design

As semiconductor manufacturing technologies push beyond 5nm and into advanced FinFET and GAA nodes, temperature inversion in VLSI has become a crucial concept for chip designers. Traditionally, designers expected circuits to slow down as temperature increased. However, due to inverse temperature dependence, this assumption no longer holds true in sub-micron designs.

In 2025, understanding how temperature inversion in VLSI affects timing, performance, and reliability is essential for every entry-level IT professional entering the world of chip design. This comprehensive guide explores what temperature inversion is, its causes, formulas, examples, and its relationship with PVT, OCV, crosstalk, and operating conditions in VLSI.

What is Temperature Inversion in VLSI?

Temperature inversion in VLSI refers to the counterintuitive phenomenon where circuit delays decrease as temperature increases, within certain voltage ranges. This behavior contradicts the conventional expectation where higher temperatures cause increased propagation delays due to slower carrier mobility.

This phenomenon is especially noticeable in sub-45nm technologies, where threshold voltage (V<sub>th</sub>) becomes a significant factor in transistor behavior. In low-voltage regions, the decrease in V<sub>th</sub> with temperature rise dominates over the mobility degradation, resulting in faster switching times—hence, a delay inversion.

Temperature Inversion in VLSI Formula

To understand this effect mathematically, consider the delay (D) of a CMOS gate:

Where:

V<sub>DD</sub> is the supply voltage

V<sub>th</sub> is the threshold voltage

μ is the carrier mobility

As temperature increases:

V<sub>th</sub> decreases

μ decreases

In older nodes, the effect of μ dominates, leading to increased delay. But in newer nodes and low V<sub>DD</sub>, the decrease in V<sub>th</sub> outweighs the degradation in mobility, causing reduced delay with rising temperature—this is temperature inversion in VLSI.

Temperature Inversion in VLSI Example

Let’s consider a CMOS inverter operating at a low V<sub>DD</sub> of 0.6V. At room temperature (25°C), the propagation delay is measured as 100 ps. As the temperature rises to 85°C, you might expect the delay to increase. However, due to inverse temperature dependence, the delay may actually drop to 95 ps.

This behavior is the temperature inversion effect, and it must be taken into account during timing analysis and corner modeling in modern chip design.

Inverse Temperature Dependence

Inverse temperature dependence is the technical term for the behavior seen in temperature inversion. It means the delay improves (decreases) as the temperature increases, due to dynamic interaction between V<sub>th</sub> and μ.

This shift has significant implications:

Traditional PVT corners (like SS@125°C) may no longer represent the worst-case delays.

Tools need to include temperature-aware modeling for accurate static timing analysis.

PVT in VLSI and Its Relation to Temperature Inversion

PVT in VLSI stands for Process, Voltage, and Temperature variations. These are the key factors that impact circuit performance and reliability. Temperature inversion conditions exhibit a nonlinear thermal profile, where the T parameter demonstrates complex atmospheric behavior.

This means:

The worst-case delay may now occur at lower temperatures, especially at reduced voltages.

Modern chip implementation requires exhaustive analysis across process-voltage-temperature (PVT) variations to guarantee robust timing convergence.

Modern static timing analysis platforms, including PrimeTime and Tempus, support comprehensive PVT corner setup, incorporating advanced modeling for temperature inversion effects in nanometer designs.

OCV in VLSI and the Role of Temperature

OCV (On-Chip Variation) in VLSI accounts for unpredictable differences in timing paths due to manufacturing variations, voltage drops, and temperature gradients across the chip.

In 2025, temperature inversion complicates OCV analysis because:

Delays may not increase uniformly with temperature across the chip.

Some blocks may exhibit faster delays at higher temperatures, while others do not.

Designers use advanced timing libraries that include temperature-dependent delay models to account for this variability during signoff.

Propagation Delay vs Temperature

In conventional CMOS technologies, circuit propagation delay exhibited direct temperature dependence, demonstrating increased latency under elevated thermal conditions. This was true because carrier mobility decreased with rising temperature.

However, in deep sub-micron technologies, the delay curve can show a negative slope at lower voltages, due to threshold voltage reduction. This behavior represents a fundamental shift in semiconductor characteristics known as temperature inversion.

Understanding this behavior is essential when:

Selecting voltage corners for testing

Analyzing hold and setup timing

Choosing clock tree strategies

Crosstalk in VLSI and Thermal Influence

Crosstalk in VLSI refers to unwanted coupling between adjacent signal lines. This effect can worsen with temperature due to increased switching activity and reduced noise margins.

When combined with temperature inversion, crosstalk becomes harder to predict:

Some nets may delay faster at high temperatures

Others may be more prone to glitching due to reduced noise immunity

Hence, crosstalk analysis tools now incorporate temperature-aware simulations to ensure signal integrity under all thermal conditions.

Operating Conditions in VLSI and Temperature Trends

Operating conditions in VLSI include factors like:

Ambient temperature

Supply voltage

Process variations

Switching frequency

Designers must simulate chips under various operating conditions to account for temperature inversion effects, especially in mission-critical applications like aerospace, medical devices, and high-speed processors.

Testing only at high temperatures may miss worst-case paths that occur at cooler conditions, which is a direct result of the temperature inversion in VLSI.

Why Temperature Inversion Matters in 2025

As chip complexity grows and power efficiency becomes paramount, low-voltage design is now common. These conditions amplify temperature inversion effects.

Ignoring this inversion may result in:

Incorrect timing analysis

Missed timing violations

Reduced chip yield

Designers in 2025 are now expected to:

Use temperature-aware timing models

Test across non-traditional PVT corners

Implement adaptive voltage scaling techniques that account for temperature inversion effects to optimize power-performance tradeoffs.

Conclusion: Adapting to Temperature Inversion in Modern VLSI Design

In the evolving landscape of semiconductor technology, temperature inversion in VLSI stands out as a transformative shift in how engineers approach timing, power, and reliability. What was once a predictable relationship between temperature and delay has now become a complex interaction shaped by reduced supply voltages and advanced transistor structures.

As we progress through 2025, designers must embrace a new mindset—one that acknowledges inverse temperature dependence and integrates it into every stage of the design flow. From static timing analysis and PVT modeling to OCV analysis, crosstalk prediction, and verifying under various operating conditions in VLSI, the role of temperature cannot be underestimated.

Failing to account for temperature inversion can lead to incorrect timing assumptions, missed violations, and ultimately, reduced yield. To address this, today’s VLSI professionals are increasingly relying on temperature-aware tools, adaptive design methodologies, and thorough corner analysis that reflect real-world thermal behaviors.

If you’re an aspiring VLSI engineer or IT professional, now is the time to strengthen your understanding of these advanced concepts. With technologies pushing beyond 5nm and power efficiency becoming a top priority, mastering temperature inversion in VLSI is not just optional—it’s essential.

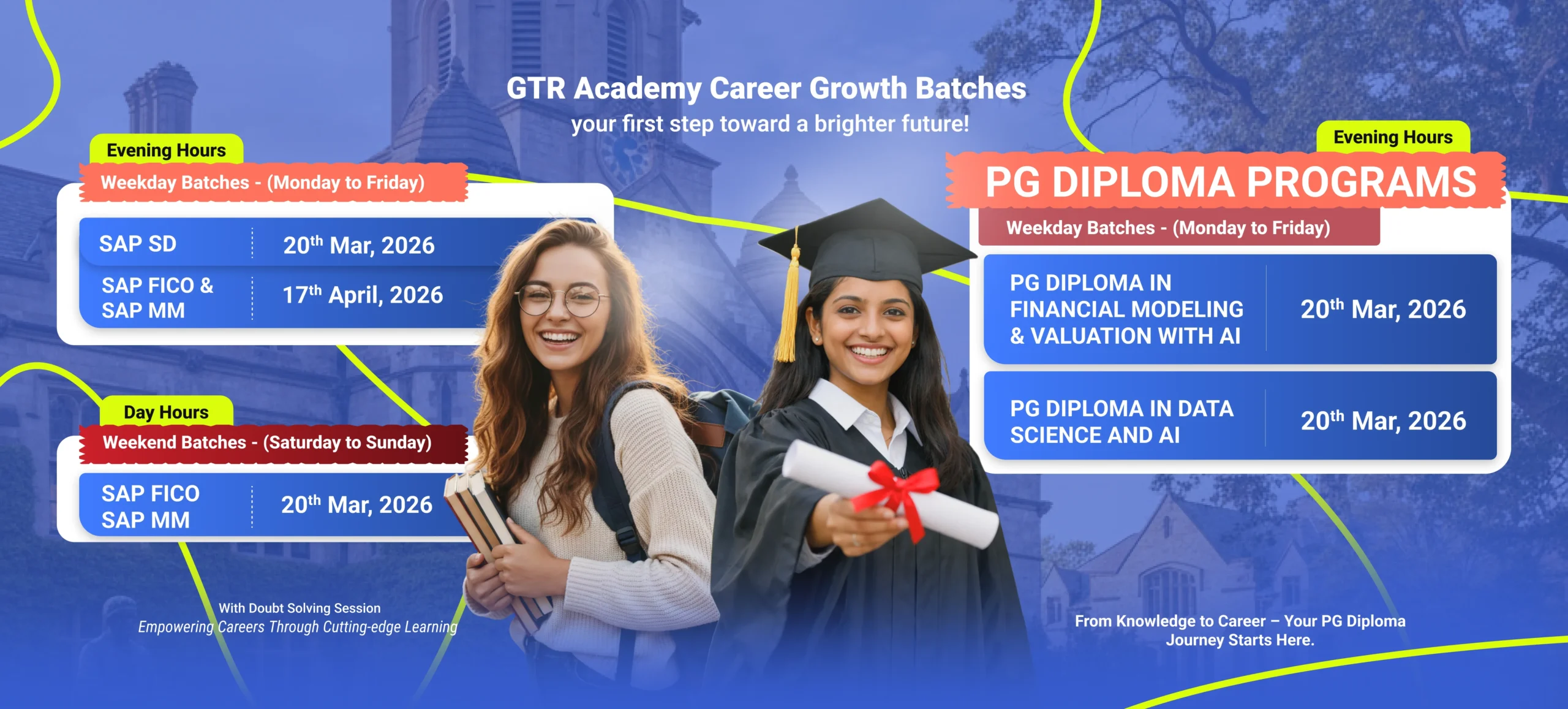

For comprehensive, hands-on training in modern chip design and analysis, consider joining GTR Academy, where industry-aligned VLSI education prepares you for the challenges of next-generation semiconductor design.

I am a skilled content writer with 5 years of experience creating compelling, audience-focused content across digital platforms. My work blends creativity with strategic communication, helping brands build their voice and connect meaningfully with their readers. I specialize in writing SEO-friendly blogs, website copy, social media content, and long-form articles that are clear, engaging, and optimized for results.

Over the years, I’ve collaborated with diverse industries including technology, lifestyle, finance, education, and e-commerce adapting my writing style to meet each brand’s unique tone and goals. With strong research abilities, attention to detail, and a passion for storytelling, I consistently deliver high-quality content that informs, inspires, and drives engagement.