IR Drop in VLSI, 2025: A Beginner’s Guide to Understanding Voltage Drops in Best Chip Design

Introduction: Why IR Drop in VLSI Matters in 2025

As the semiconductor industry continues to push the boundaries of chip performance and miniaturization, one of the key challenges faced by VLSI (Very Large Scale Integration) designers is managing IR drop in VLSI. In 2025, with advanced technology nodes like 5nm and 3nm becoming mainstream, power integrity is more crucial than ever.

For entry-level IT professionals aiming to start a career in chip design or electronic engineering, understanding IR drop in VLSI is fundamental. It impacts timing, reliability, and overall chip performance. Whether you’re working on low-power mobile SoCs or high-performance processors, ignoring IR drop can lead to critical failures in the final product.

What is IR Drop in VLSI?

The full form of IR drop in VLSI refers to the voltage drop (V = I × R) that occurs when current (I) flows through the resistive (R) power delivery network (PDN) of an integrated circuit. Essentially, this drop means that the voltage available at the far ends of the chip’s power rails is less than the voltage supplied.

The primary cause is the resistance in the power grid wires and the current consumed by transistors and logic cells. This results in the supplied voltage decreasing across the distance from the power source to the transistors, leading to potential timing failures and instability.

Types of IR Drop in VLSI

In 2025, as chips become more power-hungry yet space-constrained, it’s important to distinguish between the types of IR drop in VLSI, which are broadly categorized as:

1. Static IR Drop in VLSI

Static IR drop occurs under steady-state operating conditions, where the chip experiences a constant load. It’s generally calculated using average current values and is easier to analyze and fix.

2. Dynamic IR Drop in VLSI

Dynamic IR drop is more complex. It occurs during switching activities when there are sudden bursts of current consumption, typically in clock cycles. Dynamic IR drop in VLSI is affected by the simultaneous switching of cells and the inductance of the power delivery network.

These drops are time-dependent and harder to detect, making dynamic IR drop in VLSI a major concern in real-time chip operation.

Why is IR Drop in VLSI So Critical?

In modern chip designs, voltage margins are tighter than ever. Even small can cause:

Timing failures due to reduced voltage at the gates

Performance degradation in high-speed paths

Reduced reliability and increased risk of failure in silicon

Difficulty in meeting power and thermal budgets

Moreover, excessive IR drop can affect the signal integrity of other nets and increase leakage currents, leading to a cascading failure effect.

IR Drop in VLSI Formula

The basic IR drop in VLSI formula is derived from Ohm’s Law:

V = I × R

Where:

V is the voltage drop

I is the current drawn by the cell or block

R is the resistance of the path through the power grid

This formula is applied to thousands of nodes in a chip’s power network to simulate and verify whether the voltage levels are within acceptable limits.

Static and Dynamic IR Drop in VLSI: A Comparison

Let’s break down static and dynamic IR drop in VLSI in simple terms:

Static IR Drop reflects average load; it’s predictable and relatively easier to manage.

Dynamic IR Drop, on the other hand, results from transient current peaks. These are highly scenario-dependent and often require complex analysis using real switching patterns.

As of 2025, most leading EDA tools offer dedicated features for analyzing both types of IR drop in VLSI, making it easier for entry-level engineers to begin diagnosing these issues.

How to Fix Dynamic IR Drop in VLSI

Fixing dynamic IR drop in VLSI involves several design optimizations:

Power Grid Reinforcement

Increase the width or add more metal layers to the power grid to reduce resistance.Decap Insertion

Use decoupling capacitors to stabilize voltage supply during peak current demands.Cell Spreading

Distribute high-activity cells over a wider area to reduce current density in any single zone.Improved Floorplanning

Arrange blocks so high-current modules are closer to power pads.Clock Gating Techniques

Reduce unnecessary switching to limit transient current spikes.Dynamic Voltage Scaling (DVS)

Adjust voltage dynamically based on load requirements to prevent unnecessary drop.

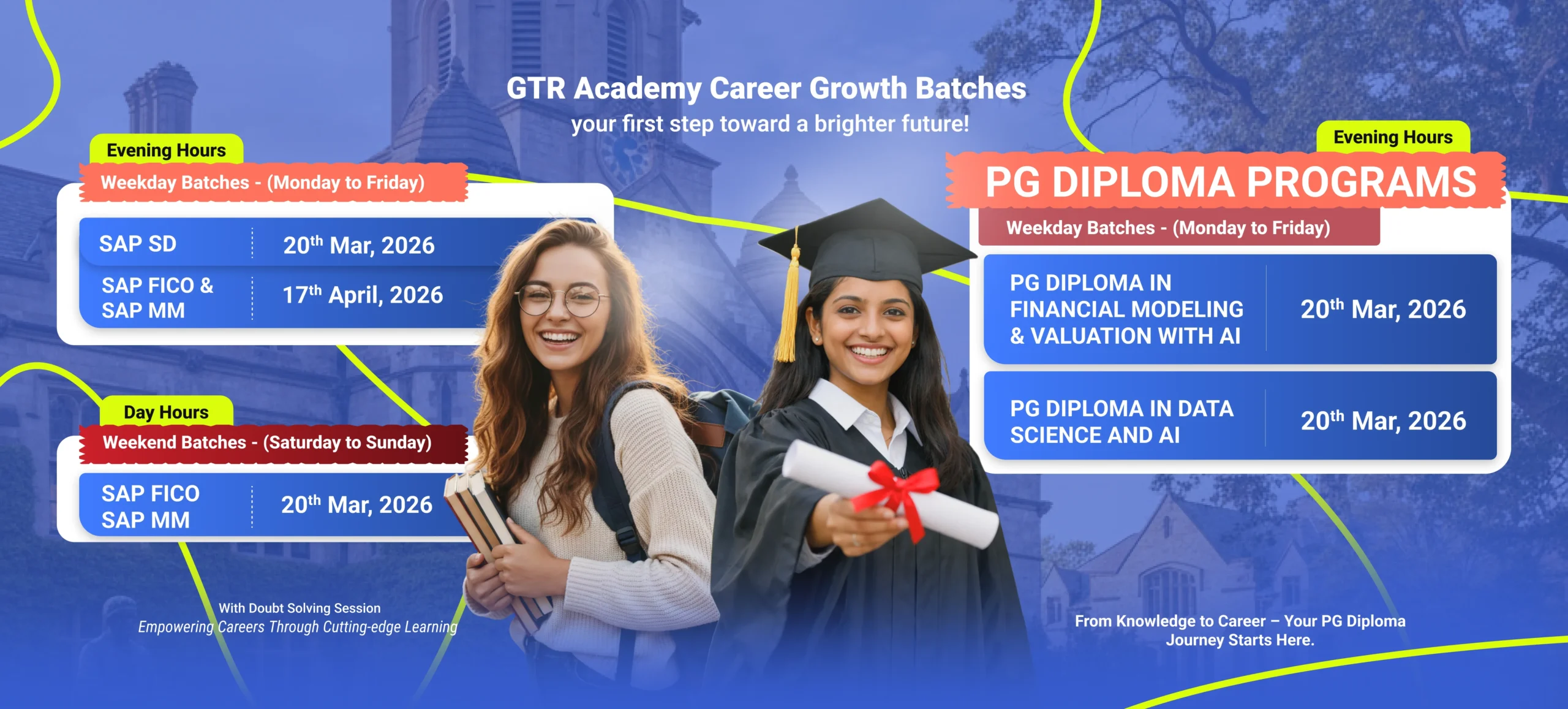

💡 At GTR Academy, our advanced courses on physical design and static timing analysis (STA) cover these techniques in-depth, preparing you for industry-ready roles.

Tools for IR Drop Analysis in 2025

The complexity of IR drop in VLSI means manual calculation is infeasible for full-chip designs. Industry-standard tools include:

Cadence Voltus

Synopsys RedHawk

Ansys Totem

Siemens mPower

These tools simulate current consumption under various operating scenarios and help identify weak spots in the power delivery network (PDN).

IR Drop in VLSI PPT and Educational Resources

For students and beginners, creating an IR drop in VLSI PPT presentation can be an excellent way to visualize the concept. These slides usually include:

Power grid architecture

Examples of static and dynamic IR drop

Diagrams showing voltage drop over distances

Formulas and real-world case studies

You can explore GTR Academy’s VLSI training programs to access curated study material, downloadable PDFs, and real-time lab simulations.

Final Thoughts: Mastering IR Drop in VLSI

The in VLSI remains one of the most pressing design challenges in semiconductor engineering, especially with high-performance and low-power designs dominating the market in 2025. By understanding the different types—static and dynamic IR drop VLSI, knowing the IR drop formula, and learning how to fix dynamic IR drop, you set a strong foundation for a successful career in the field.

✅ If you’re looking to get hands-on experience with industry tools and learn from expert faculty, offers one of the best online and offline training platforms for VLSI in India. Whether you’re a fresh graduate or a working professional, our modules are tailored to make you job-ready.

I am a skilled content writer with 5 years of experience creating compelling, audience-focused content across digital platforms. My work blends creativity with strategic communication, helping brands build their voice and connect meaningfully with their readers. I specialize in writing SEO-friendly blogs, website copy, social media content, and long-form articles that are clear, engaging, and optimized for results.

Over the years, I’ve collaborated with diverse industries including technology, lifestyle, finance, education, and e-commerce adapting my writing style to meet each brand’s unique tone and goals. With strong research abilities, attention to detail, and a passion for storytelling, I consistently deliver high-quality content that informs, inspires, and drives engagement.