Best Design for testability in vlsi – A 2025 Guide for Entry-Level Professionals

As the global demand for smarter, faster, and more compact devices continues to rise, VLSI (Very Large Scale Integration) design is becoming increasingly complex. In 2025, ensuring that each chip functions flawlessly before reaching the market is critical. This is where Design for Testability in VLSI plays a vital role.

From smartphones and IoT devices to AI processors and automotive electronics, every digital product relies on thoroughly tested semiconductor components. This blog explores what Design for Testability in VLSI means, why it’s crucial in 2025, the techniques involved, and how freshers can master it through platforms like GTR Academy.

What is Design for Testability in VLSI?

Design for Testability (DFT) in VLSI refers to incorporating special structures within a chip design that make it easier to test after manufacturing. These built-in test features allow engineers to detect and isolate faults effectively without needing complex external hardware.

In today’s high-density chips, manually debugging millions of logic gates is impractical. Without Design for Testability in VLSI, production delays, faulty components, and increased costs are inevitable. Whether you’re referring to Design for Testability in VLSI PDF, DFT books, or DFT NPTEL courses, mastering this topic is essential for a successful VLSI career.

Why Design for Testability is Essential in 2025

The year 2025 marks an explosion in demand for chips in emerging technologies like AI, 5G, robotics, and autonomous vehicles. As a result, VLSI engineers must build designs that are not only powerful and efficient but also easily testable.

Poor testability can lead to hidden design flaws that may only surface after product deployment, costing companies millions. For entry-level professionals, understanding Design for Testability techniques has become a must-have skill. Recruiters today prioritize candidates who can work on DFT implementation, scan chain design, ATPG, and Built-In Self-Test (BIST).

Searching for Design for Testability in VLSI with a diagram-based explanation or hands-on VLSI notes? You’re on the right track toward joining India’s growing semiconductor ecosystem.

Core Design for Testability Techniques in VLSI

To become proficient in DFT, you must first understand the standard techniques used in chip testing. Below are the most widely adopted Design for Testability techniques:

1. Scan Chains

A scan chain connects flip-flops in a sequential path to make it easier to shift in test patterns and observe outputs. This allows for efficient fault detection in internal logic blocks and is a foundational method in DFT.

2. Built-In Self-Test (BIST)

BIST enables a circuit to test itself by generating and analyzing its own test patterns. This eliminates the need for external testing devices, making it ideal for remote or embedded applications. BIST is a key focus area in Design for Testability in VLSI books and industry case studies.

3. Boundary Scan (JTAG)

Boundary scan, based on IEEE 1149.1, is widely used in board-level testing. It allows engineers to access I/O pins via a standardized interface, which is crucial for validating DFT-based VLSI designs.

4. Test Point Insertion

This technique involves adding additional logic points into the design to increase the visibility and controllability of internal nodes. It improves fault coverage during test pattern analysis.

5. Partial Scan vs. Full Scan

Partial scan includes selected flip-flops in the scan path, while full scan involves all flip-flops. Both approaches serve different test coverage and performance trade-offs in Design for Testability in VLSI.

If you’re exploring Design for Testability in VLSI NPTEL lectures or preparing a DFT PPT presentation, these five techniques are fundamental.

Real-Life Application of DFT in VLSI

Let’s consider a real-world scenario. Suppose an automotive control chip fails in the field due to a subtle error in the memory interface. Without embedded DFT features like scan chains or BIST, isolating the fault could take weeks in a lab. However, with DFT implemented, engineers can identify the error within hours using scan diagnostics and pattern testing.

This example proves why Design for Testability in VLSI is not just theoretical—it’s mission-critical in commercial product development.

Learning Through Notes, Diagrams, and Simulations

For students and working professionals, accessing Design for Testability in VLSI notes, diagrams, and simulations is key to building a strong foundation. Visualizing scan chains, observing test logic blocks, and simulating fault models bring clarity to complex DFT topics.

Whether you’re reviewing Design for Testability in VLSI PDFs or searching for DFT books, combining theory with hands-on learning accelerates your understanding. Institutions like GTR Academy provide real-world projects and lab exercises that simulate actual test scenarios.

Career Scope: Why DFT Skills Are in High Demand

In 2025, companies are actively hiring for roles such as:

DFT Engineer

ASIC Test Methodology Developer

Verification Engineer with Scan Expertise

RTL and ATPG Specialist

If you’re applying for internships or entry-level jobs, showcasing your ability to design scan chains, perform ATPG, and understand STA (Static Timing Analysis) gives you a distinct advantage. Employers prefer candidates with direct experience in Design for Testability in VLSI, which is why institutes like GTR Academy are becoming the top choice for skill development.

How GTR Academy Prepares You for DFT Careers

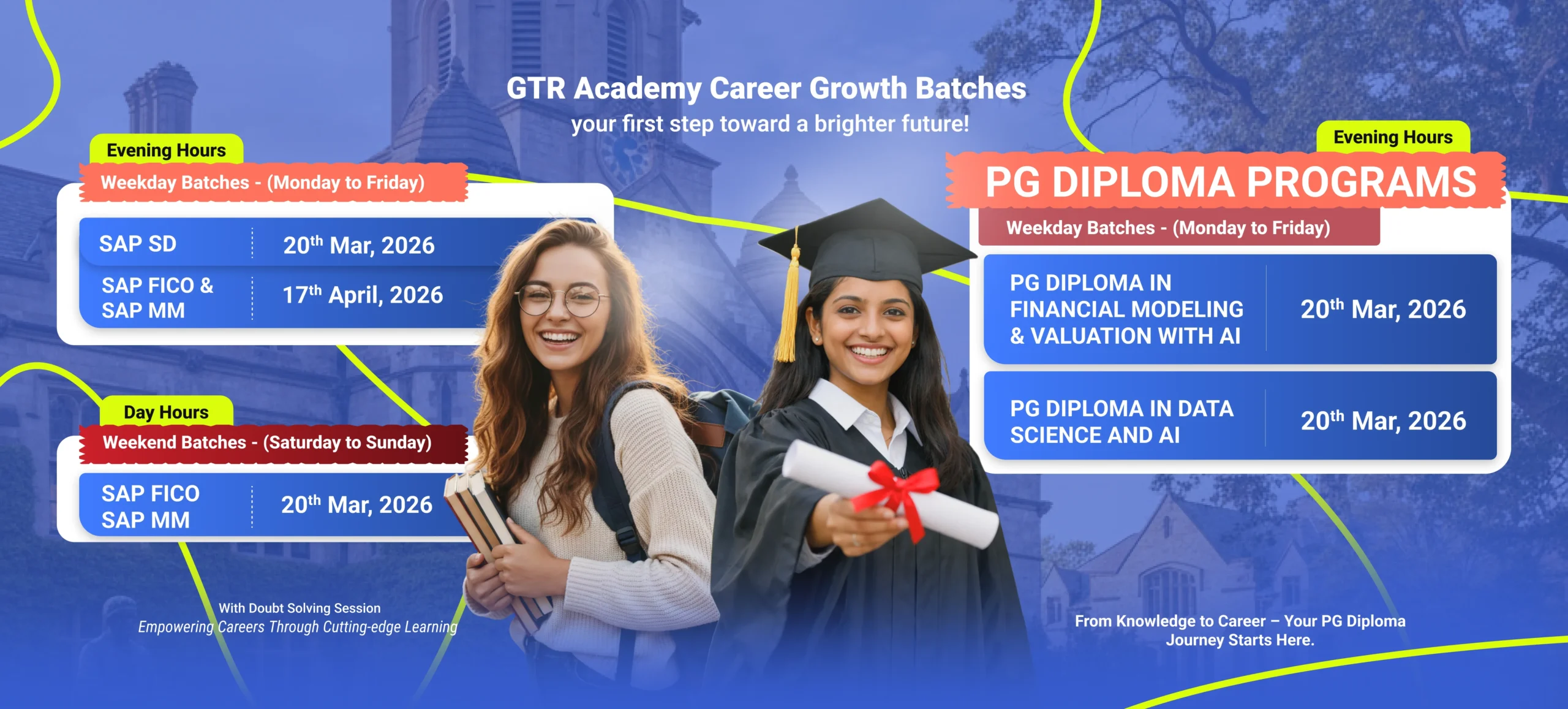

GTR Academy is a leading VLSI training institute in India that offers industry-aligned DFT training modules for freshers and working professionals.

What You’ll Learn at GTR Academy:

Scan insertion techniques and optimization

BIST design and practical implementation

ATPG simulations using Synopsys and Mentor tools

STA and timing closure strategies with DFT

Real-time ASIC project development using EDA tools

Along with technical training, GTR Academy offers resume building, mock interviews, and 100% placement support, making it a reliable launchpad for your VLSI career in 2025.

Conclusion: Embrace the Future of VLSI with DFT Expertise

Design for Testability in VLSI is more than just a skill—it’s a career-defining capability in 2025. As semiconductor designs grow more complex and the need for reliable electronics rises, DFT knowledge becomes essential for every aspiring chip designer.

Whether you’re diving into Design for Testability in VLSI books, exploring real-world examples, or taking hands-on training at GTR Academy, now is the time to build your DFT expertise. With strong demand, high salaries, and exciting job opportunities across India and globally, mastering Design for Testability in VLSI is your gateway to a successful future in chip design.

Conclusion:

Future-Proof Your VLSI Career with DFT Expertise in 2025

In the dynamic world of chip design, Design for Testability in VLSI has emerged as a crucial component for ensuring reliable and error-free semiconductors. As devices become more intelligent and compact, the role of DFT is more important than ever—especially in 2025, when the semiconductor industry is accelerating rapidly across AI, automotive, and IoT applications.