Formal Verification in VLSI, 2025: A Complete Guide for Aspiring Best Chip Designers

In the ever-evolving semiconductor industry, ensuring the correctness of chip design is critical — especially when nanometer-scale designs power everything from smartphones to satellites. This is where formal verification in VLSI steps in as a game-changer. By 2025, formal verification will be one of the most in-demand skills for VLSI professionals looking to produce error-free, optimized, and dependable integrated circuits.

This blog provides a comprehensive guide on formal verification in VLSI, including definitions, tools, real-world examples, differences from functional verification, and learning resources. If you are an entry-level IT or electronics professional planning a career in Very Large Scale Integration (VLSI), understanding formal verification is essential.

What is Formal Verification in VLSI?

Formal verification in VLSI refers to the process of mathematically proving that a design meets its specification. Rather than relying solely on simulation, formal verification uses logic-based models and proof engines to ensure the design behaves as intended under all possible input conditions.

By 2025, with the increasing complexity of SoCs (System on Chips) and ASICs, formal verification has become a standard part of the VLSI design flow in companies like Intel, Qualcomm, Synopsys, and AMD.

Why Formal Verification Matters in 2025

As transistor counts reach billions and chip functionality becomes more intricate, simulation-based verification alone is no longer sufficient. Even after thousands of simulation tests, corner-case bugs may still go undetected. Formal verification in VLSI eliminates this risk by exploring all possible conditions and ensuring logical correctness through theorem proving and model checking.

The growing need for reliability in critical systems — such as automotive safety modules, healthcare devices, and AI processors — has made formal verification tools in VLSI essential in modern chip development.

How Formal Verification Differs from Functional Verification

Beginners need to understand the difference between functional verification and formal verification in VLSI:

Functional Verification: Uses simulation-based testbenches to check if the design behaves as expected for various input scenarios.

Formal Verification: Mathematically proves correctness across all scenarios without running simulations.

Both methods are vital, but formal verification provides a new level of confidence, especially when addressing corner cases and security properties.

How Does Formal Verification Work?

The formal verification methodology in VLSI includes:

Modeling the Specification: Define what the hardware is supposed to do using a formal language.

Creating Assertions or Properties: Describe the behavior the circuit must follow.

Using a Formal Verification Tool: Apply algorithms like model checking or equivalence checking to prove the design meets the specs.

Debugging Counterexamples: If a property fails, the tool provides a counterexample pinpointing the issue.

Top Formal Verification Tools in VLSI (2025)

The year 2025 has seen powerful tool evolution in formal verification in VLSI:

Cadence JasperGold

Synopsys VC Formal

Siemens Questa Formal (Mentor Graphics)

OneSpin 360

These tools offer assertion-based verification, equivalence checking, and model checking. They’re now fully embedded in semiconductor design flows across major companies.

Real-World Examples of Formal Verification in VLSI

Let’s look at real-world applications of formal verification in VLSI design:

Control Logic in Processors: Ensure the instruction decoder doesn’t trigger invalid states.

Security Verification: Prove that secure data doesn’t leak into non-secure areas.

Finite State Machines (FSM): Ensure FSMs can’t enter undefined states.

These examples show how formal verification secures performance and safety in real hardware.

Learning Resources: Formal Verification in VLSI PDF & PPT

For freshers and professionals alike, Formal Verification in VLSI PDFs and PPTs are great study resources. These materials often include:

Introduction to formal verification

Assertion languages: SystemVerilog Assertions (SVA), Property Specification Language (PSL)

Formal verification flow diagrams

Real-world verification case studies

At GTR Academy, learners receive industry-curated PDF/PPT tutorials as part of their VLSI certification programs.

Formal Verification Tutorial: How to Learn?

If you’re new to formal verification in VLSI, start here:

Learn Digital Logic Design: Begin with Verilog/VHDL fundamentals.

Understand Assertion Languages: Master SVA and PSL.

Explore Model Checking: Study tools that analyze state machines and generate assertions.

Practice with Case Studies: Verify FIFO, arbiter, and memory controller designs.

Enroll in a VLSI Course with a Formal Verification Module: GTR Academy offers a specialized training track in this domain.

Career Opportunities After Learning Formal Verification in VLSI

By 2025, engineers skilled in formal verification techniques in VLSI are in high demand. Common roles include:

Formal Verification Engineer

ASIC Design Verification Engineer

VLSI Verification Specialist

Functional Safety Verification Engineer

Salary Outlook:

Freshers: ₹6 – ₹8 LPA

2–5 Years of Experience: ₹12 – ₹18 LPA

Top employers: Intel, AMD, Synopsys, Qualcomm, and startups in Bangalore, Noida, and Hyderabad.

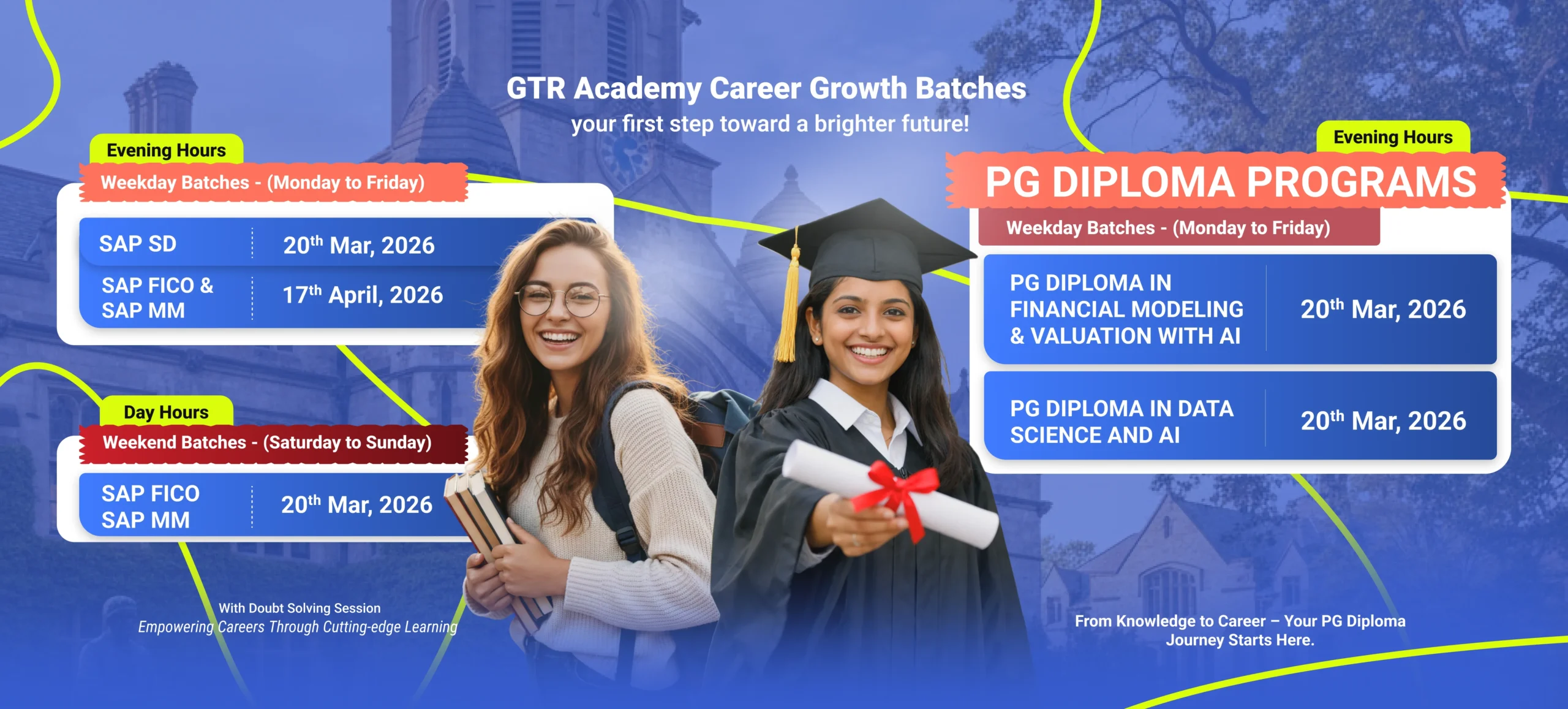

Why Learn Formal Verification at GTR Academy?

GTR Academy, one of India’s leading VLSI training institutes, provides hands-on learning designed for 2025 industry demands:

Industry-aligned curriculum

Instructor-led and recorded sessions

Project-based learning (e.g., FSM, IP verification)

Placement support with leading semiconductor companies

Access to formal verification PDFs, PPTs, and video tutorials

Affordable fee plans with EMI options

Whether you’re a fresher or IT professional transitioning to chip design, GTR Academy prepares you for real-world success.

Conclusion: Formal Verification – The Future Backbone of Reliable VLSI Design

As VLSI design grows increasingly complex in 2025, the demand for accuracy and functional safety makes formal verification in VLSI a core necessity in chip development. Unlike simulation-based methods, formal verification ensures mathematical confidence in logic correctness — under every conceivable input condition.

Whether you’re designing AI chips, secure processors, or automotive modules, mastering formal methods gives you a clear technical edge. Formal verification tools like JasperGold, VC Formal, and Questa Formal are no longer optional — they’re industry standards.

For aspiring professionals, learning formal verification techniques opens up high-paying, future-proof roles in the semiconductor ecosystem. And to gain real-world skills, GTR Academy remains a top choice in India for comprehensive VLSI education and placement support.

I am a skilled content writer with 5 years of experience creating compelling, audience-focused content across digital platforms. My work blends creativity with strategic communication, helping brands build their voice and connect meaningfully with their readers. I specialize in writing SEO-friendly blogs, website copy, social media content, and long-form articles that are clear, engaging, and optimized for results.

Over the years, I’ve collaborated with diverse industries including technology, lifestyle, finance, education, and e-commerce adapting my writing style to meet each brand’s unique tone and goals. With strong research abilities, attention to detail, and a passion for storytelling, I consistently deliver high-quality content that informs, inspires, and drives engagement.