Low Power VLSI Design in 2025: A Smart Approach to Energy

In 2025, as the world demands faster, smaller, and smarter electronic devices, the importance of low power VLSI design has become more critical than ever. With the exponential growth of mobile computing, IoT devices, wearable technology, and AI hardware, energy-efficient design isn’t just a feature—it’s a necessity.

For entry-level IT professionals and electronics engineers, understanding the need for low-power VLSI design can open up a world of career opportunities. In this blog, we explore what low-power VLSI design means in the modern era, the methods used to achieve it, and why it’s a must-have skill in 2025.

What is Low Power VLSI Design?

Low power VLSI design refers to the set of design strategies and techniques used to reduce power consumption in Very Large-Scale Integration (VLSI) circuits. These circuits are the backbone of all modern electronic devices, and power consumption affects both performance and battery life.

In simple terms, when a chip uses less power, it:

Runs cooler

Lasts longer (in battery-powered devices)

Produces less heat

Is more sustainable and cost-effective

Academic resources such as low power VLSI design books, downloadable PDFs, and structured courses like those offered by low power VLSI design NPTEL place strong focus on this subject area.

Why 2025 is the Turning Point for Low Power VLSI

In 2025, energy efficiency is a top priority in every tech domain—from smartphones to data centers and edge devices. Governments, industries, and educational institutions are emphasizing low-power VLSI design techniques to align with sustainable development goals and green technology initiatives.

Moreover, with the boom in AI chips and wearable devices, minimizing power without compromising performance has become essential. Major semiconductor companies like Intel, Qualcomm, and AMD are investing billions in low-power chip design and hiring engineers skilled in low-power VLSI design techniques.

Need for Low Power VLSI Design in 2025

The need for low-power VLSI design is driven by several real-world requirements:

Battery-Powered Devices: Mobile phones, laptops, wearables, and IoT devices must run longer without frequent charging.

Heat Management: Excessive power usage leads to heating, which reduces chip life and performance.

Sustainability: Reducing energy consumption aligns with global energy efficiency standards.

Cost Efficiency: Lower energy usage means reduced operational costs in massive data centers.

This growing demand is reflected in industry-focused learning resources such as low-power VLSI design question papers, notes, and PPT presentations that highlight its urgency.

Key Low Power VLSI Design Techniques

Clock Gating

One of the most common low-power design techniques, clock gating disables the clock to sections of a circuit not in use. This minimizes dynamic power consumption.

Power Gating

Entire sections of a chip can be powered down when inactive. This technique is used to save static (leakage) power.

Multi-Threshold CMOS (MTCMOS)

Used to reduce leakage current in standby mode, this method employs transistors with different threshold voltages for power efficiency.

Voltage Scaling

Lowering the supply voltage reduces dynamic power quadratically. It is widely used in mobile SoCs to improve battery life.

Dynamic Frequency Scaling (DFS)

It modifies the chip’s operating frequency depending on the workload to maintain an optimal balance between power consumption and performance.

Switched Capacitor Circuits

These circuits store and transfer charge efficiently and are used in analog-digital conversion blocks for lower energy operation.

Understanding and applying these methods is critical for anyone referring to low-power VLSI design notes, books, and training materials.

Learning Resources for Beginners

If you’re starting your journey in VLSI or electronics, there are plenty of resources to help you understand low-power design:

Low Power VLSI Design PDF: These downloadable notes and ebooks explain theoretical and practical concepts.

Low Power VLSI Design Book: Textbooks by Jan M. Rabaey and Gary Yeap are highly recommended for academic and industry understanding.

Low Power VLSI Design PPT: University slides provide a visual summary of core design techniques.

Low Power VLSI Design Question Papers: Practicing previous exam papers helps reinforce key design principles.

Low Power VLSI Design NPTEL: Free online courses from IITs that cover everything from transistor-level power reduction to system-level design.

Why Entry-Level IT Professionals Should Learn Low Power VLSI Design

Whether you’re from electronics, computer science, or IT, low-power VLSI design adds immense value to your technical skillset. It enables you to:

Work in top semiconductor companies

Contribute to real-world tech innovations

Understand and optimize hardware performance

Apply skills in embedded systems and chip design roles

In 2025, with the rise of fabless design houses in India and international chip design work being outsourced, professionals trained in low-power design techniques are in high demand.

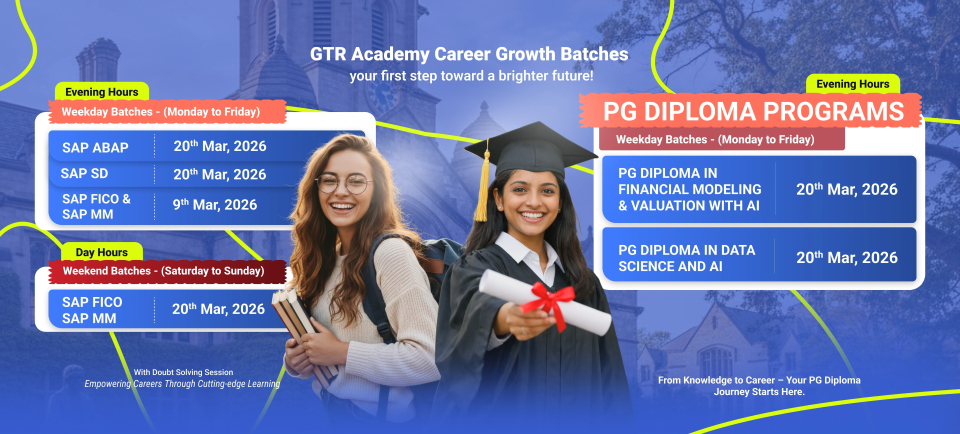

Where to Learn Low Power VLSI Design? Try GTR Academy

One of the best ways to build your VLSI foundation is through structured, industry-aligned training. GTR Academy, a trusted name in VLSI education, offers hands-on, placement-focused programs that cover:

Low-power VLSI design techniques with real-time simulation

ASIC and FPGA design modules

DFT (Design for Testability) and timing closure

Practical training on industry-standard EDA tools

Resume preparation and interview training

GTR Academy effectively connects academic knowledge with real-world industry requirements. Their personalized mentoring and exposure to real-time projects make them a preferred choice for fresh graduates and professionals alike.

To learn more about admissions, curriculum, and placements, visit GTR Academy today.

Conclusion

Low power VLSI design is not just a trend—it’s a core pillar of modern chip design. As we step into 2025, with smarter electronics and sustainability at the forefront, professionals who understand power optimization will play a key role in shaping the future of electronics.

Whether you’re a student preparing for exams using low-power VLSI design question papers or a job seeker upskilling through PDFs, books, and NPTEL, your expertise in this field will make you a valuable asset in the evolving tech landscape.